Revision 3.0

# Hirose *IT*9 ™

# **Connector System**

# **Design Notes**

Document Number: ETAD-F0842

| Section | Title                                                      | Page |

|---------|------------------------------------------------------------|------|

| 1.0     | Introduction                                               | 5    |

| 1.1     | Purpose                                                    | 5    |

| 1.2     | Scope                                                      | 6    |

| 1.3     | Application and Interpretation                             | 6    |

| 2.0     | General Information                                        | 7    |

| 2.1     | Part Number Designation/Contact Position Count Variations  | 8    |

| 2.2     | Component Weights                                          | 11   |

| 2.3     | Manufacturing Lot Number                                   | 11   |

| 2.4     | General Dimensions                                         | 12   |

| 3.0     | Operating Characteristics                                  | 13   |

| 3.1     | Material                                                   | 13   |

| 3.2     | Electrical                                                 | 13   |

| 3.3     | Mechanical                                                 | 14   |

| 3.4     | Environmental                                              | 15   |

| 1.0     |                                                            | 10   |

| 4.0     | Signal Integrity Information                               | 16   |

| 4.1     | Overview                                                   | 16   |

| 4.2     | Differential Signals                                       | 19   |

| 4.3     | PCIe Channel Example                                       | 23   |

| 4.4     | Propagation Delay                                          | 28   |

| 4.5     | Signal Integrity for FEXT Cancellation Via                 | 30   |

| 5.0     | PWB Design Information                                     | 31   |

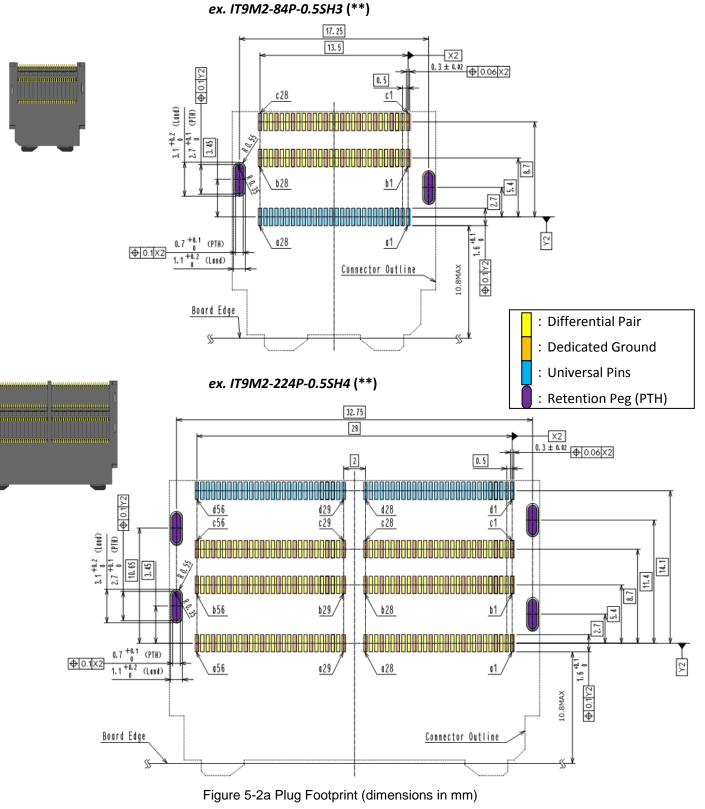

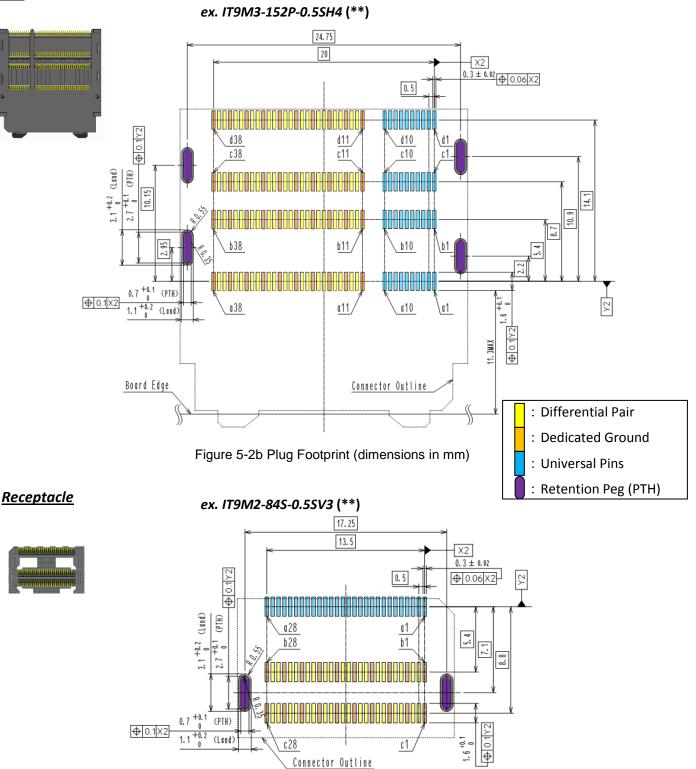

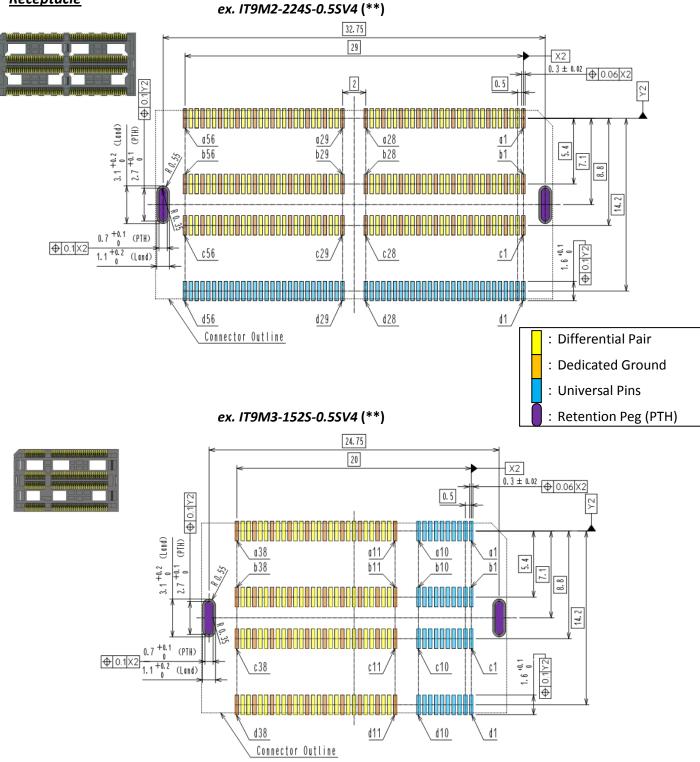

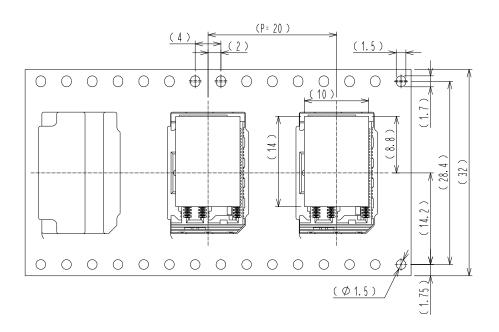

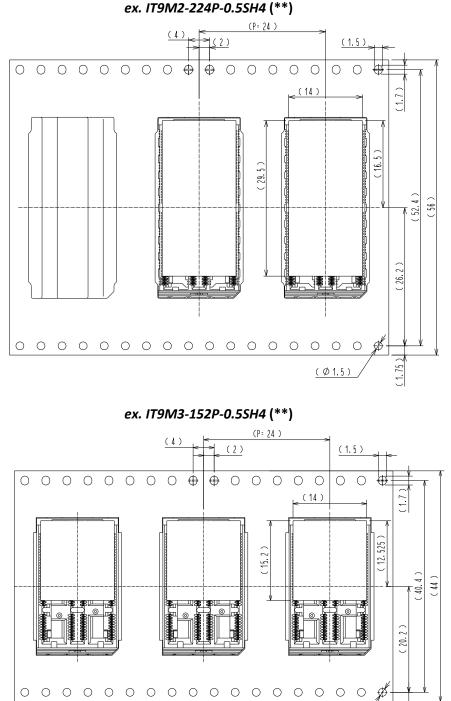

| 5.1     | Footprint                                                  | 31   |

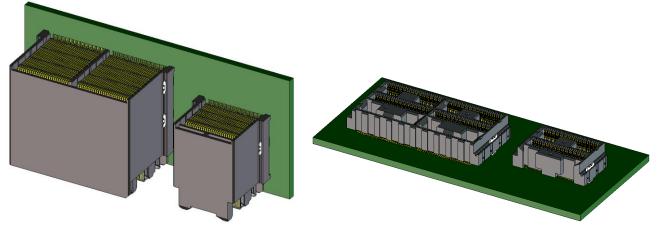

| 5.2     | Multi-Connector Systems                                    | 35   |

| 5.3     | PWB Fixing                                                 | 35   |

| 5.4     | Clearance Between Connectors and Other Components/PCB Edge | 36   |

| 5.5     | Via design, Routing Example                                | 37   |

Document Number: ETAD-F0842

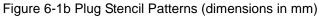

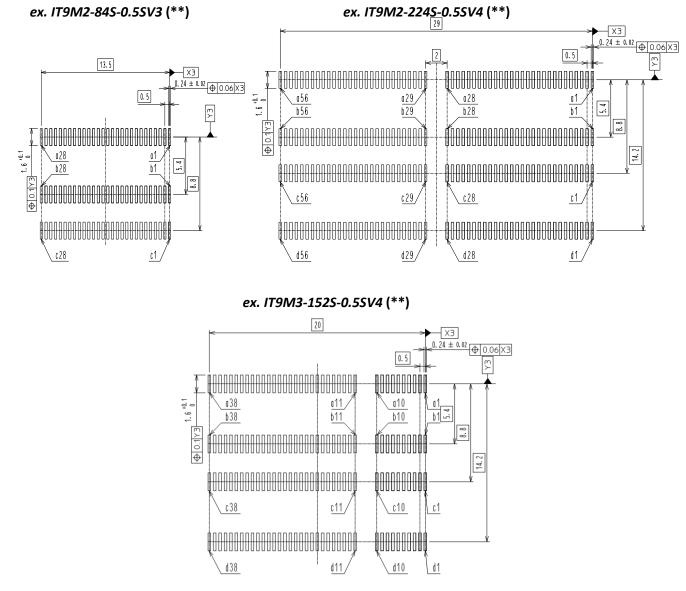

| 6.0  | Stencil Printing Information                  | 39 |

|------|-----------------------------------------------|----|

| 6.1  | Solder Paste Selection                        | 39 |

| 6.2  | Recommended Stencil Design                    | 39 |

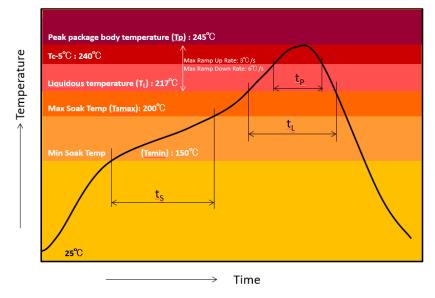

| 7.0  | Pick and Place Information                    | 42 |

| 7.1  | Packaging                                     | 42 |

| 7.2  | Pre-bake                                      | 45 |

| 7.3  | Pick Point                                    | 45 |

| 7.4  | Polarity                                      | 46 |

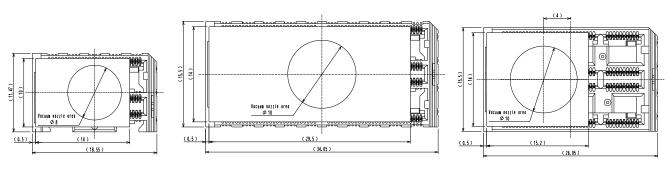

| 7.5  | Mounting Tolerances                           | 46 |

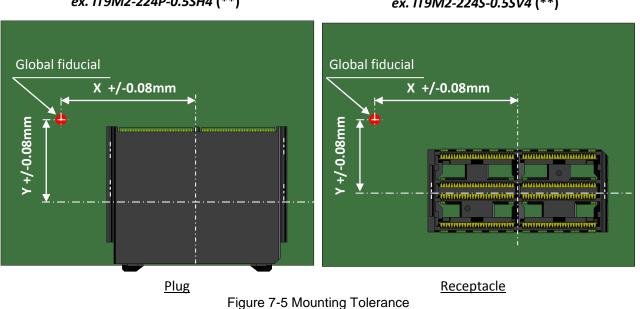

| 8.0  | Reflow and Solder Bath Processing Information | 47 |

| 8.1  | Reflow Profile for Lead-free Solder           | 47 |

| 8.2  | Other Important Factors                       | 48 |

| 8.3  | Nitrogen Environment                          | 48 |

| 8.4  | Solder bath Information                       | 48 |

| 9.0  | Assembly Processing Information               | 49 |

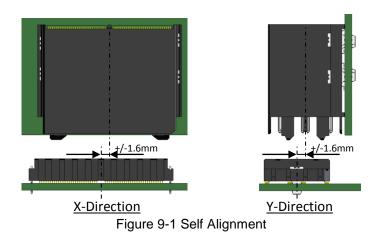

| 9.0  | Mating Self Alignment                         | 49 |

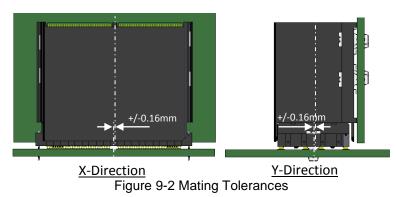

| 9.1  | Mated State Tolerances                        | 49 |

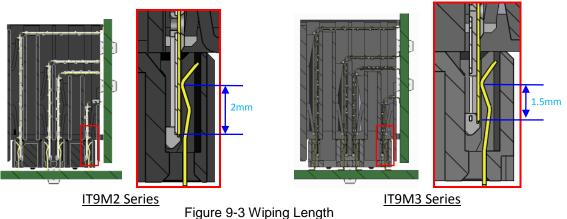

| 9.2  | Wiping Length                                 | 50 |

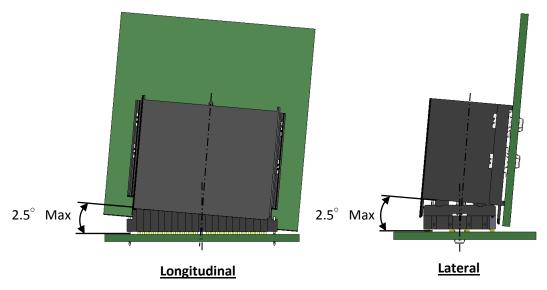

| 9.3  | Overall Assembly and Disassembly Process      | 50 |

| 9.4  |                                               | 50 |

| 10.0 | Technical Document Library                    | 51 |

| 10.1 | Technical Data                                | 51 |

| 10.2 | Technical Document                            | 51 |

RS

Document Number: ETAD-F0842

### **DESIGN NOTES**

| Revision<br>No. | Description (Major changes)         | Date                       |

|-----------------|-------------------------------------|----------------------------|

| 0.2             | Draft                               | May.28 <sup>th</sup> ,2018 |

| 1.0             | Initial release                     | Jun.25 <sup>th</sup> ,2018 |

| 2.0             | Lot No. indication change           | Jan.07 <sup>th</sup> ,2019 |

|                 | Recommended Rework Condition Change |                            |

| 3.0             | Added product info for M3           | May.18 <sup>th</sup> ,2021 |

|                 | Added channel simulation result     |                            |

|                 | Updated SI result                   |                            |

|                 |                                     |                            |

Document Number: ETAD-F0842

# Section 1 Introduction

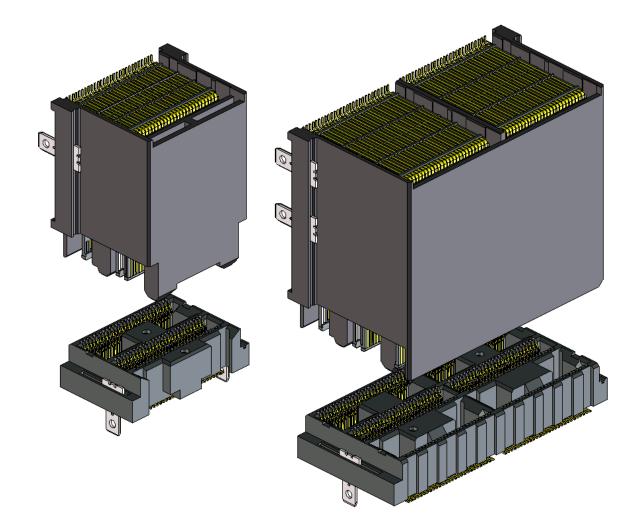

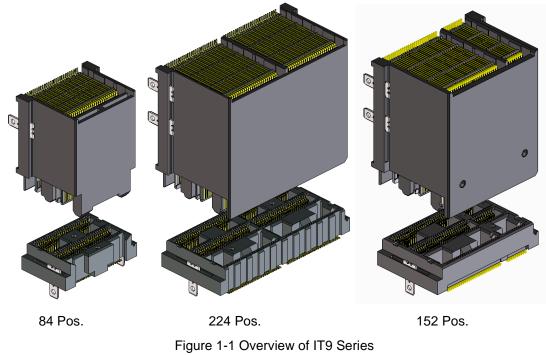

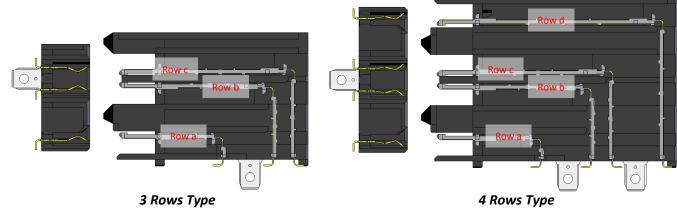

The Hirose **IT9** connector system is a two-piece type 3-row or 4-row SMT connector. Position counts of 84, 224 and 152 are available as standard variations. Please refer to individual product drawings for details.

This section of the Design Note discusses the purpose, scope, and application and interpretation.

### 1.1 Purpose

This technical bulletin is intended to provide basic information and product features of the Hirose **IT9** SMT connector system. By providing this information, Hirose believes it can help its customers to speed product development, improve quality and reliability, and limit overall system costs.

Document Number: ETAD-F0842

#### 1.2 Scope

This guideline provides information useful for applications using the **IT9** SMT connector system. It provides information pertaining to:

- a) General Information

- b) Operating Characteristics

- c) Signal Integrity Information

- d) PWB Design Information

- e) Stencil Printing Information

- f) Pick and Place Information

- g) Reflow Processing Information

- h) Assembly Processing Information

This document will be updated by Hirose as required to reflect current technologies and manufacturing capabilities. Please refer to individual product drawings for details.

#### 1.3 Application and Interpretation

This technical bulletin is intended to offer only general guidance and design concepts to customers. It does not limit customer designs nor guarantee results under all situations. Development of actual designs is the responsibility of each customer. Customers should consult with Hirose regarding their specific application, when, or if, any questions arise relating to these guidelines. Use of this technical bulletin is at customer's sole risk. This bulletin is provided "AS IS" and without warranty of any kind and HIROSE **expressly disclaims** all warranties, express or implied, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose. HIROSE does not warrant that the guidelines contained in this bulletin will meet any customer's requirements. Furthermore, HIROSE does not warrant or make any representations regarding the use or the results of the use of information contained in this bulletin in terms of correctness, accuracy, reliability, or otherwise. Under no circumstance shall HIROSE or its directors, officers, employees or agents be liable for any incidental, special or consequential damages (including damages for loss of business, loss of profits, business interruption, loss of business information and the like) arising out of the use of the information contained in this bulletin Document Number: ETAD-F0842

# Section 2 General Information

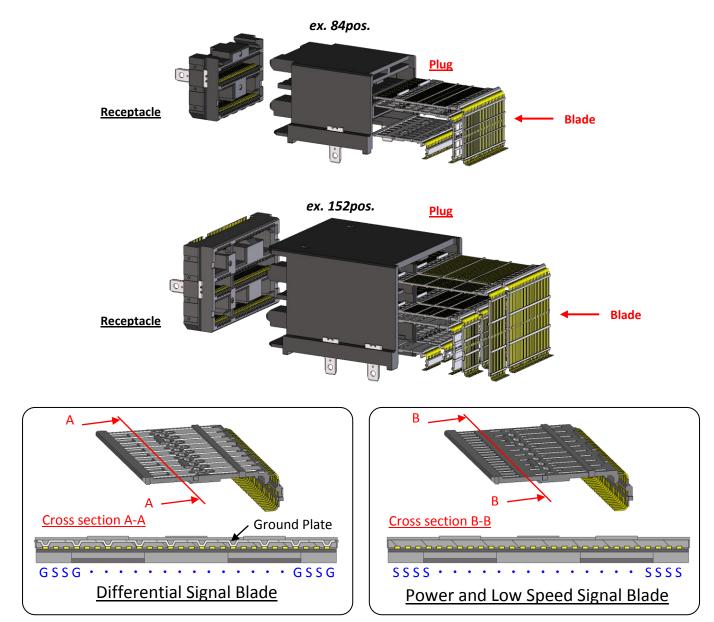

*Hirose's* **IT9** *connector system is designed to provide modular high-speed differential, single-ended and power transmission for vertical board connection.*

IT9 plug side connector is built up with two types of blades- differential signal blades and power and low speed signal blades. Differential blades consist of ground plate and signal contacts, and each signal pairs are surrounded by ground.

#### Document Number: ETAD-F0842

This section discusses part number designation, position count variations, component weights, manufacturing lot number, and general dimensions.

#### 2.1 Part Number Designation / Contact Position Count Variations

#### 2.1.1 Part Number Designation

Table 2-1 Part Number Designation

|            | Plug Side                                       | Receptacle Side                         |

|------------|-------------------------------------------------|-----------------------------------------|

| <u> 11</u> | <u> 9Mx - xP - 0.5</u> SHx (xx)                 | <u>IT9Mx - xS - 0.5</u> SVx (xx)        |

|            | <b>(1) (2)</b> (3) <b>(4)</b> (5) <b>(6)(7)</b> | <b>(1) (2)</b> (3) <b>(4)</b> (5)(6)(7) |

|            |                                                 |                                         |

| (1)        | Series name                                     |                                         |

|            | 2 : IT9M2 Series                                |                                         |

|            | 3 : IT9M3 Series                                |                                         |

| (2)        | Contact Positions                               |                                         |

|            | 84 : 84 pos.                                    |                                         |

|            | 224 : 224 pos.                                  |                                         |

|            | 152 : 152 pos.                                  |                                         |

| (3)        | Connector Gender                                |                                         |

|            | P : Male (Plug)                                 |                                         |

|            | S : Female (Receptacle)                         |                                         |

| (4)        | Contact Pitch: 0.5                              |                                         |

|            | No Further Designation                          |                                         |

| (5)        | Contact Type                                    |                                         |

|            | SH : Right Angle Type                           |                                         |

|            | SV : Vertical Type                              |                                         |

| (6)        | Row Count                                       |                                         |

|            | 3 : 3 Rows (84 Pos. only)                       |                                         |

|            | 4 : 4 Rows (224, 152 Pos.)                      |                                         |

| (7)        | Specification Number                            |                                         |

|            | Blank : Standard specification.                 | See Table 2-3 for pin assignments.      |

|            | (xx) : Different options such as                | blade combination, plating, packaging,  |

|            | or customer specifics. Refer to                 | individual drawings.                    |

Document Number: ETAD-F0842

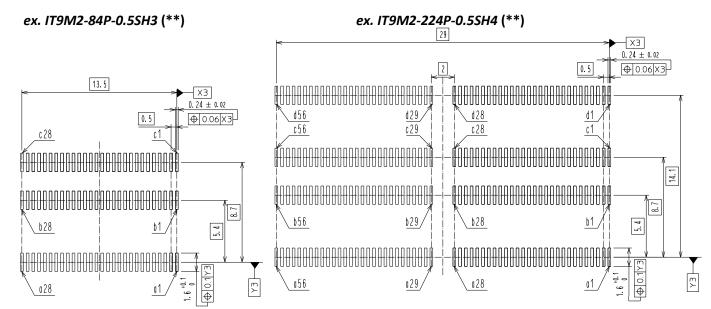

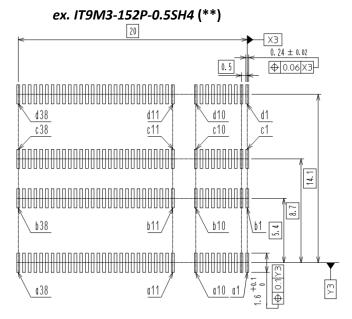

2.1.2 Contact Position Count Variations

Table 2-2 Contact Position Count Variations

| Contact Positions | Plug                   | Receptacle             |

|-------------------|------------------------|------------------------|

| 84                | IT9M2-84P-0.5SH3 (**)  | IT9M2-84S-0.5SV3 (**)  |

| 224               | IT9M2-224P-0.5SH4 (**) | IT9M2-224S-0.5SV4 (**) |

| 152               | IT9M3-152P-0.5SH4 (**) | IT9M3-152S-0.5SV4 (**) |

#### 2.1.3 Pin Assignment

#### Table 2-3 Pin Assignment

#### <3 Rows Type>

| Specifi-<br>cation | Contact   | Colu- |       |      | Pin Number                 |                                                                                                                |    |      |    |    |    |    |    |    |    |    |                             |     |      |       |       |      |     |     |     |       |     |       |   |   |

|--------------------|-----------|-------|-------|------|----------------------------|----------------------------------------------------------------------------------------------------------------|----|------|----|----|----|----|----|----|----|----|-----------------------------|-----|------|-------|-------|------|-----|-----|-----|-------|-----|-------|---|---|

| Number             | Positions | mn    | 28    | 27   | 26                         | 25                                                                                                             | 24 | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14                          | 13  | 12   | 11    | 10    | 9    | 8   |     | 6   |       | 4   | 3     | 2 | 1 |

|                    |           | Row c | G     | S    | S                          | G                                                                                                              | S  | S    | G  | S  | S  | G  | S  | S  | G  | S  | S                           | G   | S    | S     | G     | S    | S   | G   | S   | S     | G   | S     | S | G |

|                    |           | Row b | G     | S    | S                          | G                                                                                                              | S  | S    | G  | S  | S  | G  | S  | S  | G  | S  | S                           | G   | S    | S     | G     | S    | S   | G   | S   | S     | G   | S     | S | G |

|                    |           | Row a | U     | U    | U                          | U                                                                                                              | U  | U    | U  | U  | U  | U  | U  | U  | U  | U  | U                           | U   | U    | U     | U     | U    | U   | U   | U   | U     | U   | U     | U | U |

| Any                | 84        | Row   | c : F | or I | ligh                       | Spe                                                                                                            | ed | Sign | al |    |    |    |    |    |    |    | <b>S</b> :                  | Dif | fere | entia | al Si | gnal | Pin | (36 | Pin | s / 1 | 8 P | airs) |   |   |

|                    |           | Row   | b:F   | or I | High                       | h Speed SignalS: Differential Signal Pin (36 Pins / 18 Pairs)ch Speed SignalG : Dedicated Ground Pin (20 Pins) |    |      |    |    |    |    |    |    |    |    |                             |     |      |       |       |      |     |     |     |       |     |       |   |   |

|                    |           | Row   | a : F | or F | Power and Low Speed Signal |                                                                                                                |    |      |    |    |    |    |    |    |    |    | U : Universal Pin (28 Pins) |     |      |       |       |      |     |     |     |       |     |       |   |   |

Document Number: ETAD-F0842

| Specifi-<br>cation | Contact   |                          |                |              |              |            |              |              |           | n Nu | n Number |    |    |    |    |    |    |                   |      |     |     |      |       |       |    |             |    |      |    |    |

|--------------------|-----------|--------------------------|----------------|--------------|--------------|------------|--------------|--------------|-----------|------|----------|----|----|----|----|----|----|-------------------|------|-----|-----|------|-------|-------|----|-------------|----|------|----|----|

| Number             | Positions | mn                       | 28             | 27           | 26           | 25         | 24           | 23           | 22        | 21   | 20       | 19 | 18 | 17 | 16 | 15 | 14 | 13                | 12   | 11  | 10  | 9    | 8     | 7     | 6  | 5           | 4  | 3    | 2  | 1  |

|                    |           | Row d                    | U              | C            | U            | U          | U            | U            | C         | U    | U        | C  | U  | U  | U  | U  | U  | U                 | U    | U   | U   | U    | U     | U     | U  | U           | U  | U    | U  | U  |

|                    |           | Row c                    | G              | S            | S            | G          | S            | S            | G         | S    | S        | G  | S  | S  | G  | S  | S  | G                 | S    | S   | G   | S    | S     | G     | S  | S           | G  | S    | S  | G  |

|                    |           | Row b                    | G              | S            | S            | G          | S            | S            | G         | S    | S        | G  | S  | S  | G  | S  | S  | G                 | S    | S   | G   | S    | S     | G     | S  | S           | G  | S    | S  | G  |

|                    |           | Row a                    | G              | S            | S            | G          | S            | S            | G         | S    | S        | G  | S  | S  | G  | S  | S  | G                 | S    | S   | G   | S    | S     | G     | S  | S           | G  | S    | S  | G  |

|                    |           | Colu-<br>mn              | 56             | 55           | 54           | 53         | 52           | 51           | 50        | 49   | 48       | 47 | 46 | 45 | 44 | 43 | 42 | 41                | 40   | 39  | 38  | 37   | 36    | 35    | 34 | 33          | 32 | 31   | 30 | 29 |

|                    |           | Row d                    | U              | U            | U            | U          | U            | U            | U         | U    | U        | U  | U  | U  | U  | U  | U  | U                 | U    | U   | U   | U    | U     | U     | U  | U           | U  | U    | U  | U  |

| Any                | 224       | Row c                    | G              | S            | S            | G          | S            | S            | G         | S    | S        | G  | S  | S  | G  | S  | S  | G                 | S    | S   | G   | S    | S     | G     | S  | S           | G  | S    | S  | G  |

|                    |           | Row b                    | G              | S            | S            | G          | S            | S            | G         | S    | S        | G  | S  | S  | G  | S  | S  | G                 | S    | S   | G   | S    | S     | G     | S  | S           | G  | S    | S  | G  |

|                    |           | Row a                    | G              | S            | S            | G          | S            | S            | G         | S    | S        | G  | S  | S  | G  | S  | S  | G                 | S    | S   | G   | S    | S     | G     | S  | S           | G  | S    | S  | G  |

|                    |           | Row<br>Row<br>Row<br>Row | c : F<br>b : F | or H<br>or I | ligh<br>ligh | Spe<br>Spe | eed :<br>eed | Sign<br>Sigr | al<br>nal | ed S | Sign     | al |    | •  |    |    | G  | Dif<br>De<br>: Un | dica | ted | Gro | ounc | l Pir | n (60 |    | ns /<br>ns) | 54 | Pair | s) |    |

| Specifi-<br>cation | Contact   | Colu-       |     |     |      |       |      |     |      |      |    |       |      |    | Pi | n Nı | umb        | er   |      |       |       |      |       |       |       |       |      |      |    |    |

|--------------------|-----------|-------------|-----|-----|------|-------|------|-----|------|------|----|-------|------|----|----|------|------------|------|------|-------|-------|------|-------|-------|-------|-------|------|------|----|----|

| Number             | Positions | mn          |     |     |      |       |      |     |      |      |    |       |      |    |    |      |            |      |      |       | 10    | 9    | 8     | 7     | 6     | 5     | 4    | 3    | 2  | 1  |

|                    |           | Row d       |     |     |      |       |      |     |      |      |    |       |      |    |    |      |            |      |      |       | U     | U    | U     | U     | U     | U     | U    | U    | U  | U  |

|                    |           | Row c       |     |     |      |       |      |     |      |      |    |       |      |    |    |      |            |      |      |       | U     | U    | U     | U     | U     | U     | U    | U    | U  | U  |

|                    |           | Row b       |     |     |      |       |      |     |      |      |    |       |      |    |    |      |            |      |      |       | U     | U    | U     | U     | U     | U     | U    | U    | U  | U  |

|                    |           | Row a       |     |     |      |       |      |     |      |      |    |       |      |    |    |      |            |      |      |       | U     | U    | U     | U     | U     | U     | U    | U    | U  | U  |

|                    |           | Colu-<br>mn | 38  | 37  | 36   | 35    | 34   | 33  | 32   | 31   | 30 | 29    | 28   | 27 | 26 | 25   | 24         | 23   | 22   | 21    | 20    | 19   | 18    | 17    | 16    | 15    | 14   | 13   | 12 | 11 |

| A                  | 152       | Row d       | G   | S   | S    | G     | S    | S   | G    | S    | S  | G     | S    | S  | G  | S    | S          | G    | S    | S     | G     | S    | S     | G     | S     | S     | G    | S    | S  | G  |

| Any                | 152       | Row c       | G   | S   | S    | G     | S    | S   | G    | S    | S  | G     | S    | S  | G  | S    | S          | G    | S    | S     | G     | S    | S     | G     | S     | S     | G    | S    | S  | G  |

|                    |           | Row b       | G   | S   | S    | G     | S    | S   | G    | S    | S  | G     | S    | S  | G  | S    | S          | G    | S    | S     | G     | S    | S     | G     | S     | S     | G    | S    | S  | G  |

|                    |           | Row a       | G   | S   | S    | G     | S    | S   | G    | S    | S  | G     | S    | S  | G  | S    | S          | G    | S    | S     | G     | S    | S     | G     | S     | S     | G    | S    | S  | G  |

|                    |           | 4.1.5       | 4.0 |     | -    |       |      |     |      | ~    |    |       |      |    |    |      | <b>S</b> : | Dif  | fere | entia | al Si | gnal | Pin   | (72   | Pin   | s / 3 | 86 P | airs |    |    |

|                    |           | 1 to        |     |     |      |       |      |     |      |      |    | a Sig | gnai |    |    |      | G          | : De | dica | ted   | Gro   | ounc | l Pir | n (40 | ) Pir | is)   |      |      |    |    |

|                    |           | 11 to       | 38  | Pin | : ⊦0 | r Hış | gn S | pee | a Si | gnal |    |       |      |    |    |      | U          | : Un | iver | sal I | Pin   | (40  | Pins  | )     |       |       |      |      |    |    |

Document Number: ETAD-F0842

#### 2.2 Component Weights

ex. IT9M2-84P-0.5SH3 (\*\*)

ex. IT9M2-84S-0.5SV3 (\*\*)

Table 2-4 Component Weight

| Contact Positions | Part Number           | Weight (g) |

|-------------------|-----------------------|------------|

| 84                | IT9M2-84P-0.5SH3(**)  | 3.7        |

| 04                | IT9M2-84S-0.5SV3(**)  | 1.0        |

| 224               | IT9M2-224P-0.5SH4(**) | 9.8        |

| 224               | IT9M2-224S-0.5SV4(**) | 2.3        |

| 152               | IT9M3-152P-0.5SH4(**) | 8.9        |

| 192               | IT9M3-152S-0.5SV4(**) | 1.9        |

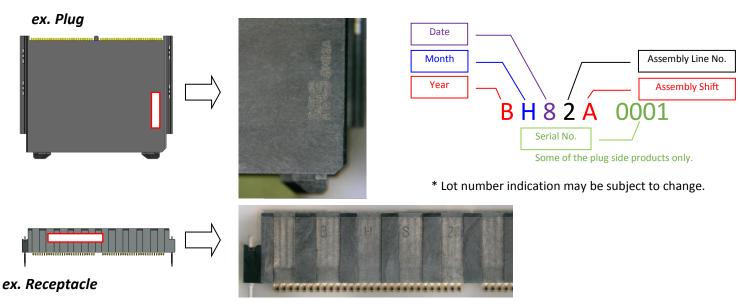

### 2.3 Manufacturing Lot Number

RS

ex. IT9M2-224S-0.5SV4 (\*\*)

ex. IT9M2-224P-0.5SH4 (\*\*)

ex. IT9M3-152P-0.5SH4 (\*\*)

ex. IT9M3-152S-0.5SV4 (\*\*)

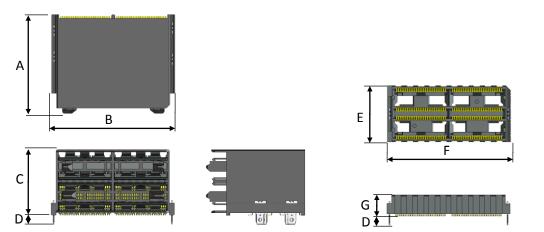

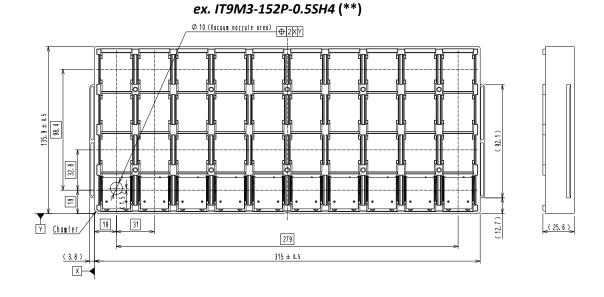

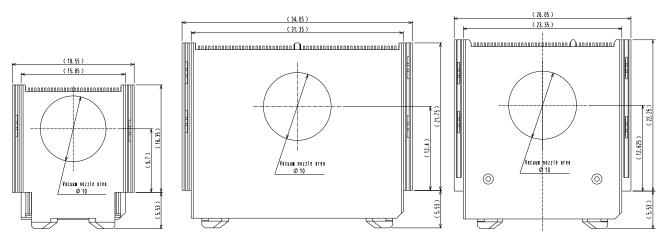

# 2.4 General Dimensions

#### Plug / Receptacle Outline

#### Table 2-5 General Dimensions

|   |                                      | Unit | Contact Positions |       |       |  |  |  |  |  |

|---|--------------------------------------|------|-------------------|-------|-------|--|--|--|--|--|

|   |                                      | Unit | 84                | 224   | 152   |  |  |  |  |  |

| Α | Plug outline length                  | mm   | 21.88             | 27.28 | 27.78 |  |  |  |  |  |

| В | Plug outline width                   | mm   | 18.55             | 34.05 | 26.05 |  |  |  |  |  |

| С | Plug height (from SMT lead)          | mm   | 14.3              | 18.1  | 18.6  |  |  |  |  |  |

| D | Retention peg length (from SMT lead) | mm   |                   | 2.5   |       |  |  |  |  |  |

| E | Receptacle outline length            | mm   | 11.47             | 15.5  | 15.5  |  |  |  |  |  |

| F | Receptacle outline width             | mm   | 18.55             | 34.05 | 26.05 |  |  |  |  |  |

| G | Receptacle height (from SMT lead)    | mm   |                   | 5.84  |       |  |  |  |  |  |

Please refer to individual product drawings for details.

Document Number: ETAD-F0842

# Section 3 Operating Characteristics

This section discusses material, electrical, mechanical, and environmental characteristics.

#### 3.1 Material

Numbering of component is same as customer drawing.

#### <u>3.1.1 Plug</u>

#### Table 3-1 Plug Material and Finish

| No. | Component     | Material        | Finish & Remarks                                                                                                   |

|-----|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------|

| 1   | Housing       | LCP             | Black , UL 94V-0                                                                                                   |

| 2   | Contact       | Copper Alloy    | Contact Area : Gold (0.76μm min) over Nickel (3.0μm min)<br>Mount Area : Gold (0.03μm min) over Nickel (1.0μm min) |

| 3   | Blade         | LCP             | Black , UL 94V-0                                                                                                   |

| 4   | Ground Plate  | Stainless Steel | -                                                                                                                  |

| 5   | Retention Peg | Copper Alloy    | Sn (3.0μm min) over Nickel (1.0μm min)                                                                             |

| 6   | Hard Tray     | HIPS            | Black                                                                                                              |

| 7   | Top Cover     | HIPS            | Black                                                                                                              |

#### 3.1.2 Receptacle

#### Table 3-2 Receptacle Material and Finish

| No. | Component             | Material     | Finish & Remarks                                                                                                   |

|-----|-----------------------|--------------|--------------------------------------------------------------------------------------------------------------------|

| 1   | Housing               | LCP          | Black , UL 94V-0                                                                                                   |

| 2   | Contact               | Copper Alloy | Contact Area : Gold (0.76μm min) over Nickel (3.0μm min)<br>Mount Area : Gold (0.03μm min) over Nickel (1.0μm min) |

| 3   | Retention Peg         | Copper Alloy | Sn (3.0μm min) over Nickel (1.0μm min)                                                                             |

| 4   | Pick Up Tape          | Nomex        | -                                                                                                                  |

| 5   | Embossed Carrier Tape | PS           | -                                                                                                                  |

| 6   | Top Cover Tape        | PS           | -                                                                                                                  |

### 3.2 Electrical

#### Table 3-3 Electrical Test Conditions and Requirements

| Test                                        | Test Condition                       | Requirement                                                                                      | Typical Value                                                                 |

|---------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Low Level Contact<br>Resistance*<br>(LLCR)  | EIA-364-23                           | 60mΩ max (*1) (Row A)<br>70mΩ max (*1) (Row B)<br>80mΩ max (*1) (Row C)<br>90mΩ max (*1) (Row D) | Ex. 224pos.<br>(Row A) 27.0mΩ (Row B) 42.0mΩ<br>(Row C) 45.6mΩ (Row D) 64.8mΩ |

| Insulation Resistance<br>(IR)               | EIA-364-21                           | 100MΩ min                                                                                        | Ex. 224pos.<br>2.00E+05MΩ                                                     |

| Dielectric<br>Withstanding Voltage<br>(DWV) | EIA-364-20<br>AC 150V for 60 seconds | No flashover or breakdown                                                                        | Ex. 224pos.<br>No flashover or dielectric breakdown<br>was found              |

\* The value of contact resistance includes contact point and the bulk resistance.

### Document Number: ETAD-F0842

#### 3.3 Mechanical

#### Table 3-4 Mechanical Test Conditions and Requirements

| Test                            | Test Condition                                                                                                       | Requirement                                                                                                                                  | Typical Value                                                                                                     |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Insertion /<br>Withdrawal Force | EIA-364-13                                                                                                           | Insertion Force : 0.4 N/pin max<br>Withdrawal Force : 0.015 N/pin max                                                                        | Ex. 84pos. IF/WF : 21.2/10.3N<br>Ex. 224pos. IF/WF : 58.6/31.1N                                                   |  |

| Mechanical Operation            | EIA-364-09<br>Cycle rate: 300 max per hour<br>100 times                                                              | <ol> <li>Contact resistance change :<br/>10mΩ or less</li> <li>No damage, crack, or looseness of parts</li> </ol>                            | Ex. 224pos.<br>(Row A) <+10mΩ (Row B) <+10mΩ<br>(Row C) <+10mΩ (Row D) <+10mΩ                                     |  |

| Random Vibration                | EIA-364-28<br>Frequency:20 TO 500Hz<br>Power Special Density:0.02G <sup>2</sup> /Hz<br>for 60 min in 3 directions    | <ol> <li>No electrical discontinuity of         <ol> <li>μ s or more</li> <li>No damage, crack, or looseness of parts</li> </ol> </li> </ol> | No electrical discontinuity of 1 $\mu$ s or more was found.<br>No damage, crack, or looseness of parts were found |  |

| Packing                         | ISTA-3A                                                                                                              | No evidence of physical damage<br>SMT Coplanarity : 0.13mm max                                                                               | Ex. 224pos.<br>No evidence of physical damage<br>was found.<br>SMT Coplanarity : <0.13mm                          |  |

| Contact Normal Force            | 0.45<br>0.4<br>0.35<br>0.3<br>0.25<br>0.2<br>0.15<br>0.1<br>0.05<br>0.1<br>0.15<br>0.2<br>0.05<br>0.1<br>0.15<br>0.2 | 0.2N min                                                                                                                                     | 0.45N<br>9M2-224S-0.5SV4                                                                                          |  |

| Contact<br>Wiping Length        | IT9M2 Series : 2.0 +/-0.3 mm<br>IT9M3 Series : 1.5 +/-0.3 mm                                                         | -                                                                                                                                            |                                                                                                                   |  |

| Retention Force                 | 0.5N min / Signal contact<br>2.0N min / Retention peg                                                                |                                                                                                                                              | Ex.224pos.Receptacle<br>Signal contact : 2.78N<br>Retention peg : 8.82N                                           |  |

| SMT Coplanarity                 | 0.13 mm max                                                                                                          |                                                                                                                                              | -                                                                                                                 |  |

Document Number: ETAD-F0842

#### 3.4 Environmental

Based on accelerated high temperature tests that store connectors at 105 °C for more than 120 hours according to EIA-364-1000.01, the **IT9** can be stored for up to 10 years. Refer to Table 3-5 for the environmental standards and conditions that the **IT9** has been tested to meet.

The **IT9** has been tested and meets the requirements for environmentally-related corrosive atmosphere according to EIA-364-65. These test procedures demonstrate how plated and unplated surfaces react when exposed to different concentrations of flowing gas mixtures.

#### Table 3-5 Environmental Test Conditions and Requirements

| Test                             | Test Condition                                                                                                                                                                                             | Requirement                                                                                                           | Remarks |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------|

| Thermal Shock                    | EIA-364-32 Condition I<br>Temperature (°C): -55 $\rightarrow$ 20 ~ 35 $\rightarrow$ 85 $\rightarrow$ 20 ~ 35<br>Time (min): 30 $\rightarrow$ 5 max $\rightarrow$ 30 $\rightarrow$ 5 max<br>Under 10 cycles | <ol> <li>Contact resistance change:<br/>+10mΩ or less</li> <li>No damage, crack, or<br/>looseness of parts</li> </ol> | -       |

| Cyclic Temperature &<br>Humidity | EIA-364-31<br>@ 25°C, 90~95% RH:120 min Dwell time<br>↓ 120 min Ramp time<br>@ 65°C , 90~95% RH:120 min Dwell time<br>Under 60 cycles                                                                      | <ol> <li>Contact resistance change:<br/>+10mΩ or less</li> <li>No damage, crack, or<br/>looseness of parts</li> </ol> | -       |

| Dry Heat                         | EIA-364-17<br>Exposed at 105 °C, 300h                                                                                                                                                                      | <ol> <li>Contact resistance change:<br/>+10mΩ or less</li> <li>No damage, crack, or<br/>looseness of parts</li> </ol> | -       |

| Mixed Flowing Gas                | EIA-364-65<br>Exposed at 30°C, 70% RH<br>Cl <sub>2</sub> : 10ppb, NO <sub>2</sub> : 200ppb, H <sub>2</sub> S: 10ppb, SO <sub>2</sub> : 100ppb<br>Mated 10 days                                             | 1) Contact resistance change:<br>+10mΩ or less<br>2) No heavy corrosion                                               | -       |

| Dust                             | EIA-364-91<br>Unmated 1 hour                                                                                                                                                                               | Contact resistance change:<br>+10mΩ or less                                                                           | -       |

**IT9** Connector System Document Number: ETAD-F0842

# Section 4 Signal Integrity Information

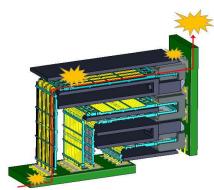

This section contains the overview, 32 Gbps solution, differential performance, a full-channel simulation of a PCIe environment using, and propagation delay of Hirose's **IT9** signal integrity performance, as well as an introduction of Hirose's patented FEXT cancellation via structure.

#### 4.1 Overview

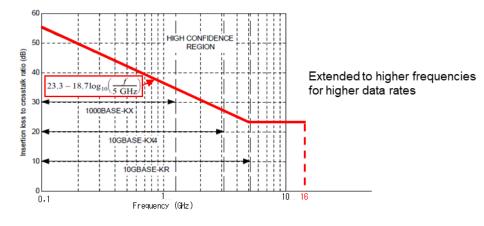

The IT9 minimizes signal loss and crosstalk by adopting a unique enhanced GND design (Figure 2-1). As a result, IT9 is able to meet the stringent (enhanced) insertion loss-to-crosstalk ratio (ICR) specifications specified in IEEE802.3ap up to 16GHz (=32Gbps).

Figure 4-1 ICR Specification

#### <IT9M2 Series>

Actual measurements were taken with IT9M2-84P<sup>1</sup> and 84S connectors, transitions through outer routing layers, and micro strip traces de-embedded (Figure 4-2).

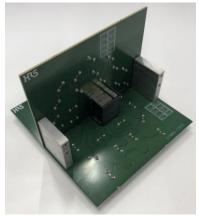

Figure 4-2 SI Test board

<sup>&</sup>lt;sup>1</sup> Row-a modified to differential signal blade for measurement

#### Document Number: ETAD-F0842

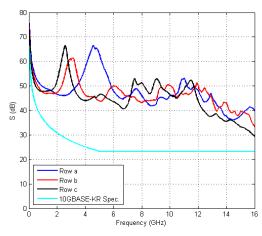

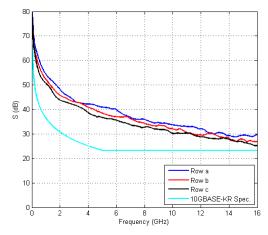

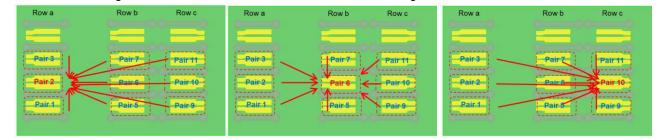

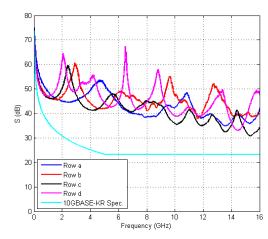

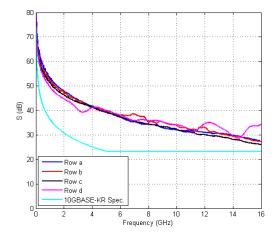

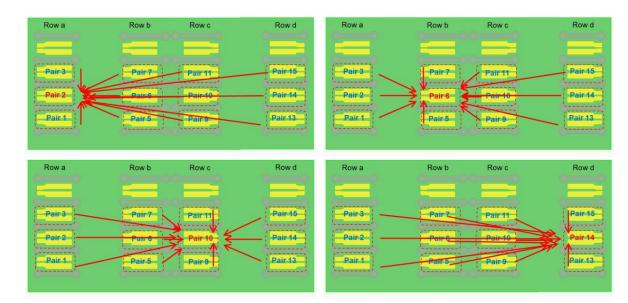

The following ICR curves correspond to the power sum of NEXT<sup>2</sup> (Figure 4-3) and FEXT <sup>3</sup>(Figure 4-4) from 8 aggressor pairs and 1 victim pair in 3 columns of IT9-84P/S. It is clear that **IT9M2** meets the ICR spec. for 32 Gbps data rate in a populated configuration (Figure 4-5).

Figure 4-3 ICR with 8 NEXT

Figure 4-4 ICR with 8 FEXT

Figure 4-5 Populated Pin Configuration

#### <IT9M3 Series>

Actual measurements were taken on test boards with IT9M3-152P and 152S connectors, transitions through surface layer, and coplanar traces de-embedded. (Figure 4-6)

Figure 4-6 SI Test board

<sup>2</sup> near-end crosstalk

<sup>3</sup> far-end crosstalk

#### Document Number: ETAD-F0842

The following ICR curves correspond to the power sum of near-end crosstalk (Figure 4-7) and far-end crosstalk (Figure 4-8) from 11 aggressor pairs and 1 victim pair in 4 columns of IT9-152P/S. It is clear that **IT9M3** meets the ICR spec. for 32 Gbps data rate in a populated configuration (Figure 4-9).

Figure 4-7 ICR with 11 NEXT

Figure 4-8 ICR with 11 FEXT

Figure 4-9 Populated Pin Configuration

Document Number: ETAD-F0842

#### 4.2 Differential Signals

#### <IT9M2 Series>

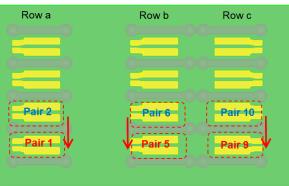

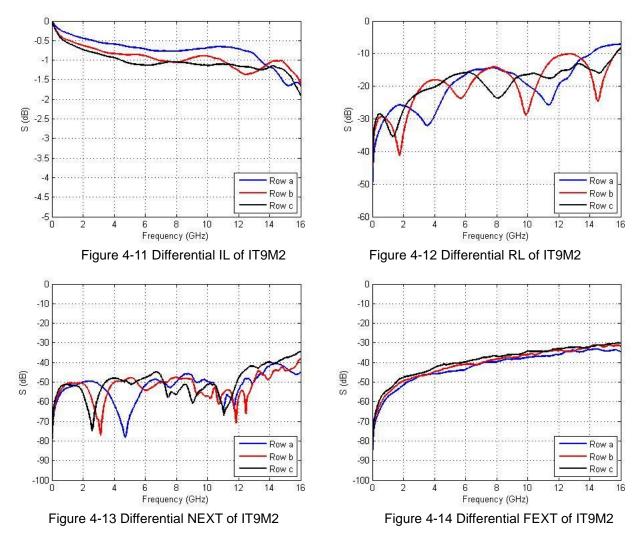

Figures 4-11 to 4-14 show the measured differential insertion loss (IL), return loss (RL), NEXT, and FEXT between two nearest neighbors for each row (Figure 4-10).

Figure 4-10 Nearest neighbors of IT9M2

#### Document Number: ETAD-F0842

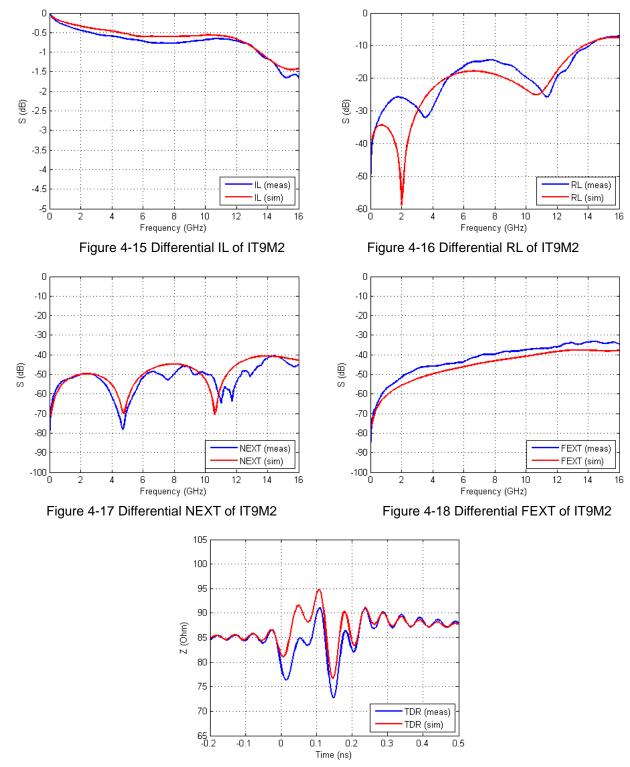

Figures 4-15 to 4-19 show the measured vs. simulated differential IL, RL, NEXT, FEXT between two nearest neighbors in Row a, and impedance.

RS

Document Number: ETAD-F0842 <IT9M3 Series>

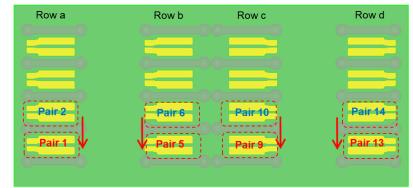

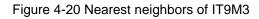

Figures 4-21 to 4-24 show the measured differential IL, RL, NEXT, FEXT between two nearest neighbors for each row (Figure 4-20).

#### Document Number: ETAD-F0842

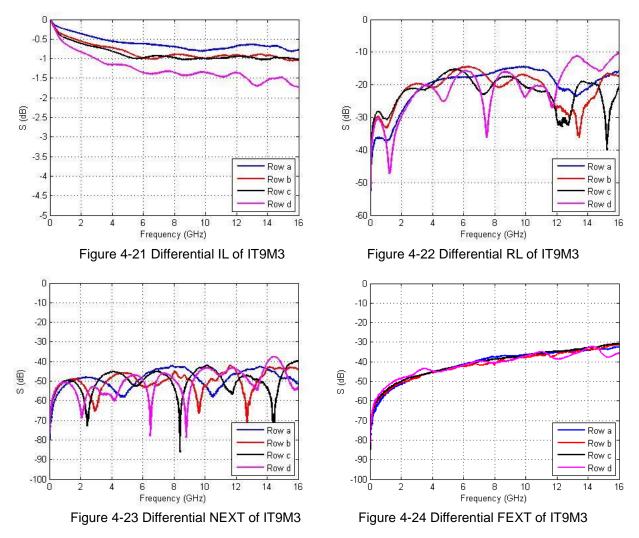

Figures 4-25 to 4-29 show the measured vs. simulated differential IL, RL, NEXT, FEXT between two nearest neighbors in Row a, and impedance.

RS

#### Document Number: ETAD-F0842 4.3 PCIe Channel Example

#### <u>4.3.1 Overview</u>

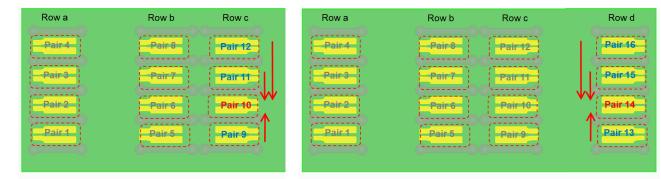

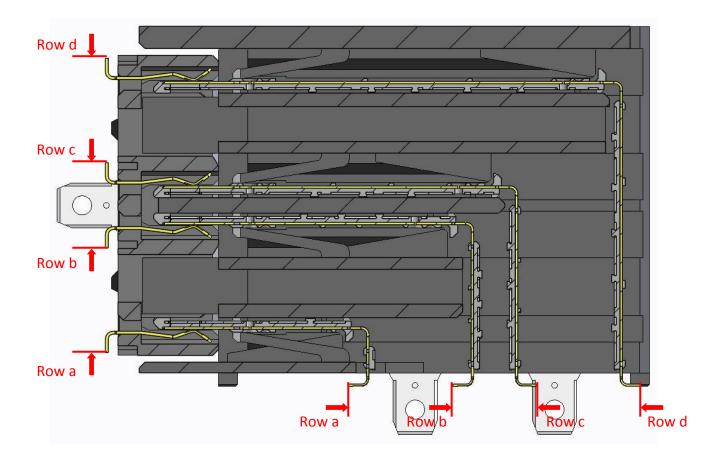

This section will demonstrate the feasibility of IT9's use within a PCIe Gen4 and 5 environment through full-channel simulations using Seasim Ver.0.78. A one-connector topology was examined, with the focus being on just the Row C and Row D channels for IT9M2 and IT9M3 respectively (Figure 4-30) for the sake of brevity, based on the assumption that longer channels will have higher loss thus smaller eye openings.

Figure 4-30 Each row examined with three aggressors from the same row (left: IT9M2, right: IT9M3)

#### 4.3.2 PCIe4.0/5.0 Compliance Specification

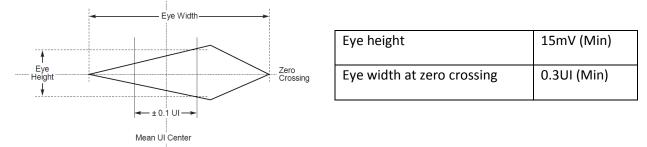

Section 8.5.1.4.3 of the PCI Express Base Specification, Rev. 5.0, Version 1.0 characterizes the pass/fail of a channel with the following eye mask (Figure 4-31), with the minimum compliance limit of the eye height defined as 15mVpp and the eye width as 0.3UI for both Gen4 and 5

Figure 4-31 Pass/Fail eye mask as defined in PCIe 4.0/ 5.0 Base Specification (pg 1082-1084)

#### 4.3.3 Channel Simulation

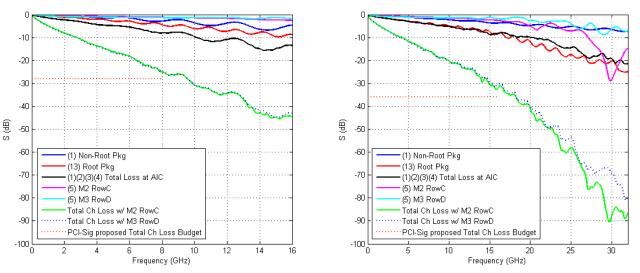

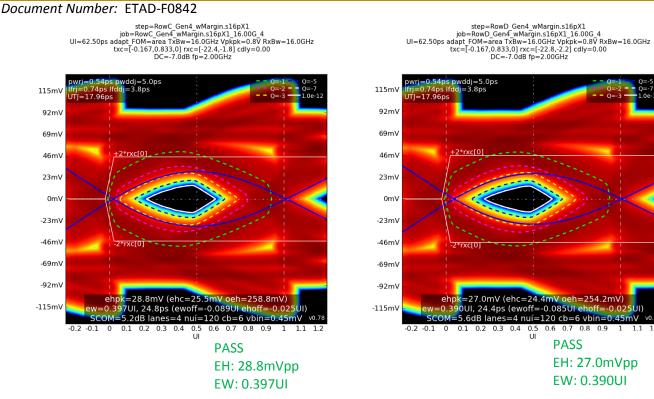

As an examination of the feasibility of IT9 application within a PCIe4.0/5.0 channel, full-channel simulation models were created following the topology seen in Figure 4-32. Included components follow the loss curves shown in Figure 4-33 to fit within the loss budgets proposed by the PCI-Sig work group. Both the PCIe4.0 and 5.0 simulation models refer to the stack-up shown in Figure 4-33 at both the System Board and Add-in Card, with FEXT-cancellation vias (see Section 4.5) going from L1 to L24. The resulting eye diagrams produced through Seasim simulation (Figure 4-36 and 4-37) were examined with 3 aggressors as seen in Figure 4-30 and the adapt/equalizer configuration seen in Figures 4-34 and 4-35.

### SIGNAL INTEGRITY

Document Number: ETAD-F0842 Cu Thick. Cu Foil (mils) wt (oz) 2.00 .5 oz 1 Tx Package DK Foil .5 oz Prepreg I-Speed 3313(59) 4.17 3.73 0.60 0.5 oz 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 3.77 0.60 0.5 oz 6.71 Prepreg I-Speed 1078(69.5)/1078(69.5 0.60 0.5 oz 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 0.60 0.5 oz 3.73 3.81 Prepreg I-Speed 3313(59) 0.60 0.5 oz 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 0.60 0.5 oz 3.73 4.04 Prepreg I-Speed 3313(59) 0.60 0.5 oz 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 24681012 vias 0.60 0.5 oz Prepreg I-Speed 1078(69.5)/1078(69.5) 3.50 6.71 10 0.60 0.5 oz ③ AIC Trace 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 11 0.60 0.5 oz Prepreg I-Speed 1078(69.5)/1078(69.5) 3.50 6.71 12 0.60 0.5 oz 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 13 0.60 0.5 oz Prepreg I-Speed 3313(59) 3.73 4.04 14 0.60 0.5 oz (5) IT9M2/IT9M3 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 0.60 0.5 oz 15 3.50 6.71 Prepreg I-Speed 1078(69.5)/1078(69.5) 0.60 0.5 oz 16 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 3.77 0.60 0.5 oz 17 (1) Cap Lead-out 6.71 Prepreg I-Speed 1078(69.5)/1078(69.5) 3.50 18 0.60 0.5 oz 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 3.77 Trace ⑦ Cap Lead-in 0.60 0.5 oz 19 3.73 4.04 Prepreg I-Speed 3313(59) 0.60 0.5 oz Trace Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 3.77 4.00 13 Rx Package 0.60 0.5 oz 21 3.73 3.81 Prepreg I-Speed 3313(59) 9 AC Cap 0.60 0.5 oz 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 0.60 0.5 oz 3 50 6.71 Prepreg I-Speed 1078(69.5)/1078(69.5) 0.60 0.5 oz 3.77 4.00 Core I-Speed 4.00mils 3313 0.5 oz / 0.5 oz 18.5Gx24.5 0.60 0.5 oz 25 tem Board 4.17 Prepreg I-Speed 3313(59) Foil .5 oz 3.73 2.00 .5 oz

Figure 4-32 High-level diagram for the 16.0GT/s and 32.0GT/s example channels (left). Both the System Board and AIC for the two channels follow the stack-up shown (right)

Figure 4-33 Components in the channel (left: for 16GT/s Gen4, right: for 32GT/s Gen5)

#### Document Number: ETAD-F0842

| E Seasim-0.78 - Gen4_16ports.sea (root_dir: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | :\Python26\seasim-release-0.78\Projects\11-1 — 🛛 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Seasim-0.78 - Gen4_16ports.sea (root_                                                                                                                                                                                                                                                                                                                                                                                                            | dir: C:\Python26\seasim-release-0.78\Projects\11-1 — 🛛 🗙                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Include                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | File Include                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                           |

| Main S-Parameters Jitter/Noise Adapt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Equalizers Step Responses Configuration Sweep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Main S-Parameters Jitter/Noise Ad                                                                                                                                                                                                                                                                                                                                                                                                                | apt Equalizers Step Responses Configuration Sweep                                                                                                                                                                                                                                                                                                                         |

| Adaptation FOM<br>Include xtalk during adaptation<br>Treat PS/DE lists as pairs<br>Tx pre-shoot search space (priority) (dB)<br>Tx coefficient search space (priority) (dB)<br>Tx coefficient search space<br>Max Tx EQ boost (dB)<br>LEQ1 DC gain search space (dB)<br>LEQ1 DC gain search space (dB)<br>LEQ2 DC gain search space (dB)<br>LEQ2 DC gain search space (dB)<br>LEQ2 pole search space (Hz)<br>DFE taps and max magnitude (V)<br>Max ratio between dfe0 and h0<br>Data sample offset search space (UI) | area  brown and an area of DFE taps  brown and brown an | If no adaptation EQ can be explicitly set to<br>Tx pre-shoot (priority) (dB)<br>Tx de-emphasis (priority) (dB)<br>Tx EQ FIR coefficients<br>LEQ1 DC gain (dB)<br>LEQ1 pole (Hz)<br>LEQ2 DC gain (fixed HF gain of LEQ)<br>LEQ2 DC gain (dB)<br>LEQ2 pole (Hz)<br>LEQ2 AC gain (fixed HF gain of LEQ))<br>Rx bandwidth (Hz) (1st pole)<br>Rx bandwidth (Hz) (2nd pole)<br>LEQ response relative path<br>LEQ response cPickle file of pole/gain/Hz | 0.0         0.0           0.0         0.0           [1]         0.0           0.0         0.0           0.0         0.0           0.0         0.0           0.0         0.0           0.0         0.0           0.0         0.0           0.0         0.0           16e9         # HF roll-off of equalizer           0.0         0.0           LEQ_responses         0.0 |

| Ratio of UI used for PDA adaptation 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LEQ response indices                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                         |

| Adapt eye-width using no-dfe eye                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Adapt eye-width using no-dfe eye                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | [0]                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data sample offset (UI)                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.0                                                                                                                                                                                                                                                                                                                                                                       |

Figure 4-34 Seasim Adapt (left) and Equalizers (right) configurations for PCIe4.0 16GT/s simulation

| Seasim-0.78 - Gen5_16ports.sea (root_dir: C                                                | 🗄 Python26\seasim-release-0.78\Projects\11-1 — 🔲 🗙     | Seasim-0.78 - Gen5_16ports.sea (root_c                                      | lir: C:\Python26\sea | sim-release-0.78\Projects\11-1 — | - 🗆 × |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|----------------------------------|-------|

| File Include                                                                               |                                                        | File Include                                                                |                      |                                  |       |

| Main S-Parameters Jitter/Noise Adapt                                                       | Equalizers Step Responses Configuration Sweep          | Main S-Parameters Jitter/Noise Ad                                           | apt Equalizers g     | Step Responses Configuration Sv  | veep  |

| Adaptation FOM<br>Include xtalk during adaptation                                          | area v                                                 | If no adaptation EQ can be explicitly set b<br>Tx pre-shoot (priority) (dB) | elow<br>0.0          |                                  |       |

| Treat PS/DE lists as pairs                                                                 |                                                        | Tx de-emphasis (priority) (dB)                                              | 0.0                  |                                  |       |

| Tx pre-shoot search space (priority) (dB)                                                  | [] # Disable PS adaptation                             | Tx EQ FIR coefficients                                                      | [1]                  |                                  |       |

| Tx de-emphasis search space (priority) (dB)                                                | [] # Disable DE adaptation                             | LEQ1 DC gain (dB)                                                           | 0.0                  |                                  |       |

| Tx coefficient search space                                                                | 24 # Coefficent space size                             | LEQ1 pole (Hz)                                                              | 0.0                  |                                  |       |

| Max Tx EQ boost (dB)                                                                       | 8.0 # Maximum Tx EQ boost in dB for Cspace search      | LEQ1 AC gain (fixed HF gain of LEQ)                                         | 0.0                  |                                  |       |

| LEG1 DC gain coarch coarch (dP) range(=15 =4.1) # DC gain of CTLE in dP                    |                                                        | LEQ2 DC gain (dB)                                                           | 0.0                  |                                  |       |

| LEQ1 pole search space (Hz)                                                                | [9.5e9] # Fp2 CTLE pole location                       | LEQ2 pole (Hz)                                                              | 0.0                  |                                  |       |

| LEQ2 DC gain search space (dB)                                                             | [0.0] # DC gain of CTLE2 in dB                         | LEQ2 AC gain (fixed HF gain of LEQ))                                        | 4.35                 | # Fp1=1.65*Fz1 in dB             |       |

| LEQ2 pole search space (Hz)                                                                | [742.5e6] # Fp1=Fz1*1.65 CTLE2 pole location           | Rx bandwidth (Hz) (1st pole)                                                | 28e9                 | # Fp3 HF roll-off of equalizer   |       |

| DFE taps and max magnitude (V)                                                             | [0.06]+[0.02]*2 # Number and dynamic range of DFE taps | Rx bandwidth (Hz) (2nd pole)                                                | 28e9                 | # Fp4 HF roll-off of equalizer   |       |

| Max ratio between dfe0 and h0                                                              | 0.8 # Max ratio between h1/h0 for dfe tap0             | LEQ response relative path                                                  | LEQ_responses        |                                  |       |

| Data cample offset search search (III) arange(-0.3.0.05.0.05) # Edge to data sample offset |                                                        | LEQ response cPickle file of pole/gain/Hz                                   |                      |                                  |       |

| Ratio of UI used for PDA adaptation                                                        |                                                        | LEQ response indices                                                        | n                    |                                  |       |

| Adapt eye-width using no-dfe eye                                                           |                                                        | DFE tap values (V)                                                          | [0]                  |                                  |       |

|                                                                                            |                                                        | Data sample offset (UI)                                                     | 0.0                  |                                  |       |

Figure 4-35 Seasim Adapt (left) and Equalizers (right) configurations for PCIe5.0 32GT/s simulation

RS

### SIGNAL INTEGRITY

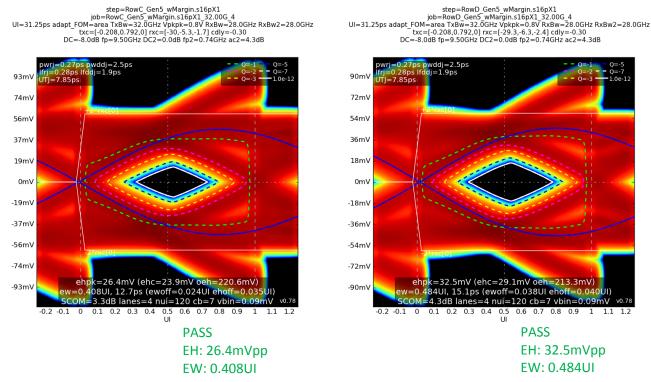

Figure 4-37 32GT/s Eye for channel incorporating IT9M2 RowC (left) and IT9M3 RowD (right)

Document Number: ETAD-F0842

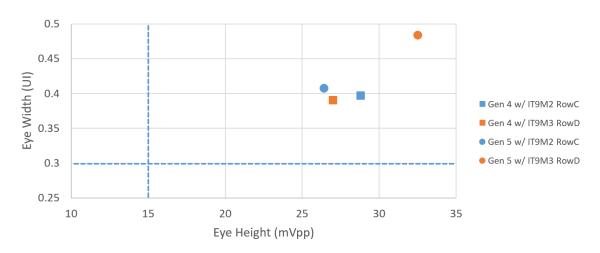

#### 4.3.4 Comments on Feasibility

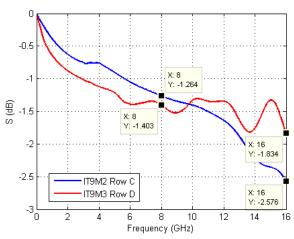

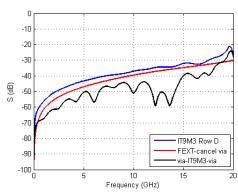

Through analysis of the channel simulation results observed in Section 4.3.3 of this document (summarized in Table 4-1 and Figure 4-38), it can be safely concluded that it is possible to adopt both IT9M2 and IT9M3 into working PCIe4.0 16.0 GT/s channel, as can also be said for PCIe5.0 32.0 GT/s channel. One trend that is of note however, is the slight variance in resulting eye between the channel with IT9M2 and IT9M3. At the 16GT/s simulation, the channel using IT9M2 Row C resulted in a larger eye than with IT9M3 Row D. This relationship is flipped for the 32GT/s simulation, where the simulation using IT9M3 Row D has the larger eye. This seems to be consistent with what is observed at the connector-only performance (Figure 4-39). Comparing the IL at IT9M2 Row C and IT9M3 Row D, it can be observed that at 8GHz, the fundamental frequency for PCIe4.0, Row D is more lossy, while at 16GHz, Row C ends up becoming more lossy.

|                      | PCIe4.0 (16GT/s)<br>EH (mV <sub>pp</sub> ) EW (UI) |       | PCle5.0 (32GT/s)       |         |

|----------------------|----------------------------------------------------|-------|------------------------|---------|

|                      |                                                    |       | EH (mV <sub>pp</sub> ) | EW (UI) |

| IT9M2 Series (Row C) | 28.8                                               | 0.397 | 26.4                   | 0.408   |

| IT9M3 Series (Row D) | 27.0 0.390                                         |       | 32.5                   | 0.484   |

Figure 4-39 Comparison of Connector-only performance between IT9M2 Row C and IT9M3 Row D

Document Number: ETAD-F0842

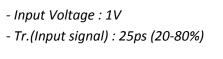

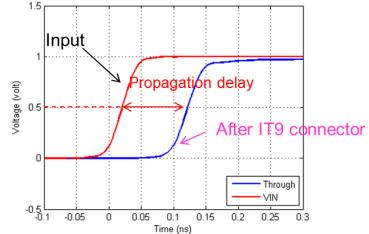

#### 4.4 Propagation Delay

#### 4.4.1 Propagation Delay Overview

Each blade in **IT9** has different length, shown in 4.4.2 Please be aware of the signal distance difference when designing *PWB*.

#### 4.4.2 Signal Path Length

Figure 4-40 IT9 Cross Section

Document Number: ETAD-F0842 4.4.3 Propagation Delay for IT9

#### Fig4-41 Propagation Delay

#### <IT9M2 Series (84,224 Pos.)>

|                                     | Inner row |        |        | Unit   |      |

|-------------------------------------|-----------|--------|--------|--------|------|

|                                     | Row a     | Row b  | Row c  | Row d  | Onic |

| Circul worth lowerth                | 17660     | 28460  | 32620  | 43420  | μm   |

| Signal path length                  | 695.3     | 1120.5 | 1284.3 | 1709.4 | mils |

| Propagation delay<br>- Single ended | 115.6     | 170.85 | 193.49 | 256.56 | ps   |

| Propagation delay<br>- Differential | 110.56    | 164.43 | 186.3  | 249.19 | ps   |

Table 4-2 Propagation Delay for IT9M2 Series

#### <IT9M3 Series (152 Pos.)>

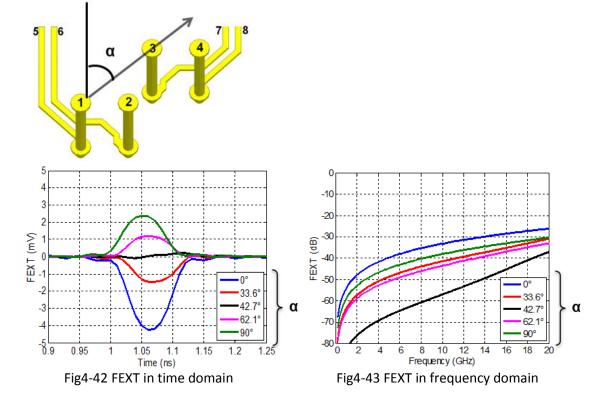

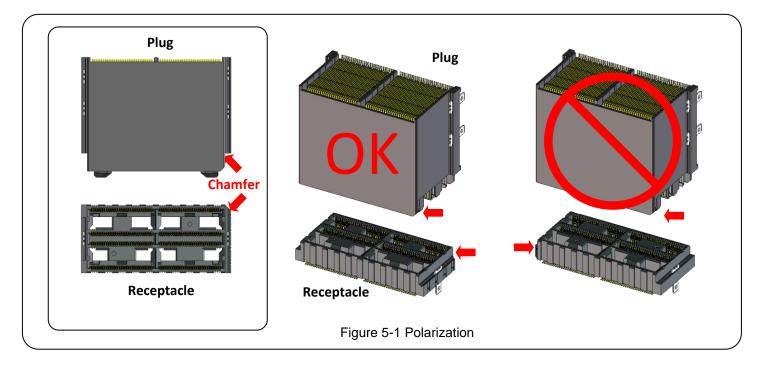

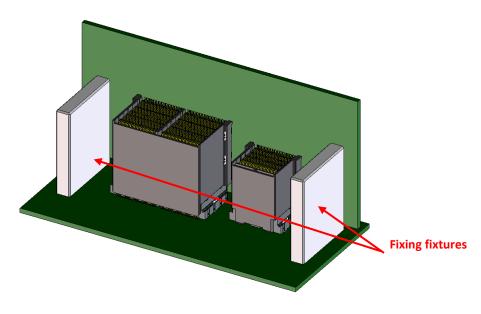

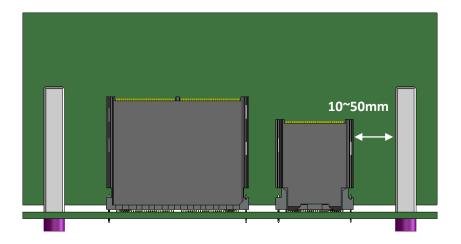

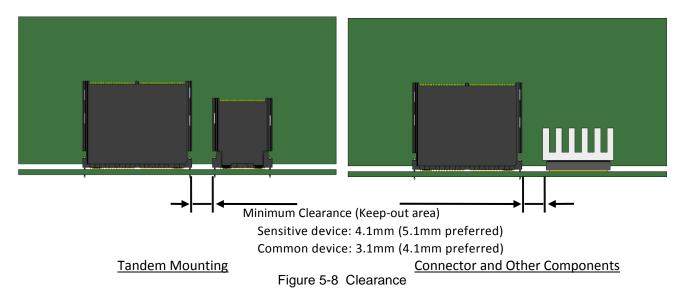

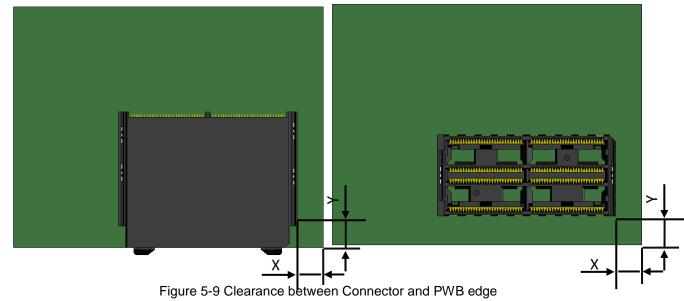

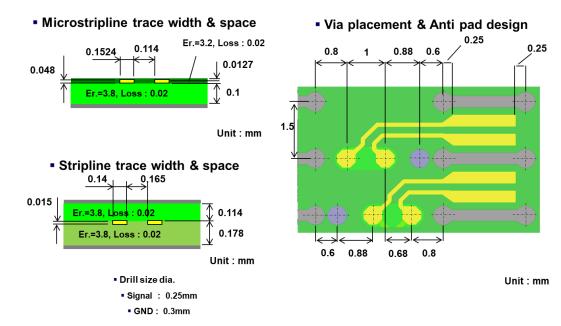

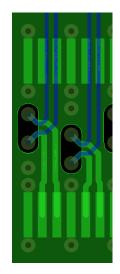

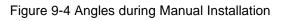

|                                     | Inner row | Inner row 🔶 Ou |         |         | Unit |